June 07, 2021

2616

What are the specific changes? DDR5 is very different from DDR4. In fact, it is more like LPDDR4. DDR5 brings 9 changes.

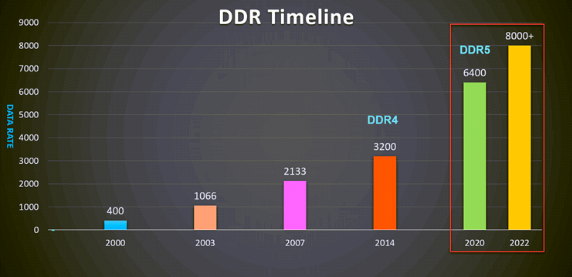

1. Faster! The first and most important one, the data rate reaches 6.4 Gbps, while DDR4 is only 3.2Gbps. There is also an item in the specification, which will push the upper speed limit to above 8 Gbps in the next few years. The channel structure is similar to LPDDR4, and there are also two independent 40-bit channels in ECC. There are also higher pre-reading, higher burst lengths, and higher rows and columns, all of which improve efficiency and realize high-speed mode.

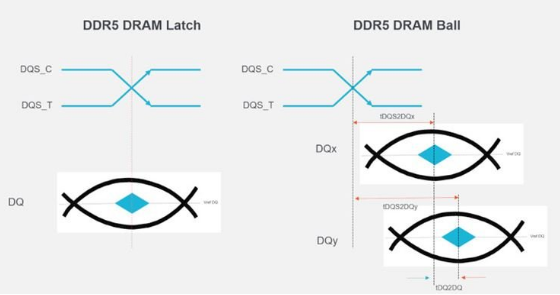

2. Another big change brought by DDR5 is that the write is no longer centered. There is a fixed offset between DQS and DQ, so we can't just measure the delay between DQS and DQ on the oscilloscope to figure out whether to read or write. It's not so easy anymore! The separation of read and write bursts will become more complicated.

3. New clock jitter measurement. DDR5 introduces Rj, Dj, and Tj measurements, instead of cycle and cycle-to-cycle jitter measurements. The Rj index becomes very tight at the maximum data rate. Excellent signal integrity becomes critical to measuring these parameters with confidence.

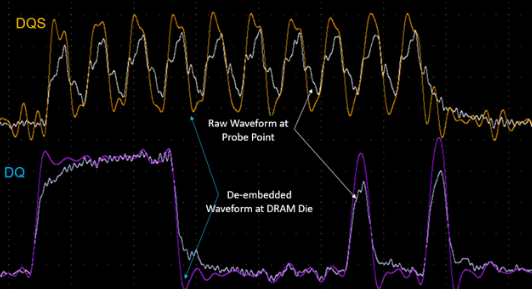

4. De-embedding will become very critical at higher DDR5 data rates. De-embedding is a technique to remove the load on the probe and interposer. It is also used to move the detection point from the DRAM ball to the DRAM chip in a virtual manner to minimize reflections. We want to see what Rx sees. In order to successfully create a de-embedding filter file or transfer function, s-par files are required, and there are a lot of them. The idea is to use s-par models in SOC packages, circuit board models, DRAM packages, interposers, probes, and IO settings, such as Tx drive strength and Rx ODT (if any), to simulate DDR channels as truthfully as possible. If there is no s-par model, simple transmission line parameters such as propagation delay and characteristic impedance can also be used, which is achieved by measuring reflections on the oscilloscope screen.

5. We will have Rx equalization, 4th order DFE in the receiver for the first time. DDR5 increases the data rate without migrating the DQ bus to differential signaling, that is, the DQ bus is still single-ended, the same as DDR3/4. However, the memory channel has a large number of impedance mismatch points, which increase the overall ISI due to reflections. When the data rate exceeds 4800 Mbps, the data eye pattern of the DRAM ball is expected to close. DDR5 DRAM Rx implements a 4th-order DFE to help equalize the DQ signal and open the data eye pattern after the receiver latches the data. In addition, RCD CA Rx also requires DFE to ensure reliable signal capture.

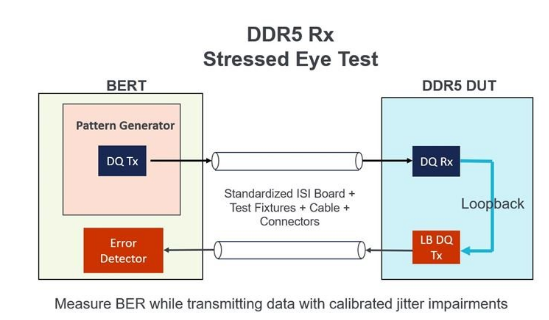

6. Another obvious change of DDR5 is to include a loopback channel. Take a look at the pin diagram of DDR5, you will find dedicated DQS/DQ loopback pins. It is used to implement independent DRAM RX/TX characterization. The loopback channel is very important. In fact, it is through the loopback channel that we know what bit decisions the receiver really makes in real time. It is a single wire shared between all different receivers. Due to poor signal integrity and other reasons, we can only send back every fourth or every second bit, so there is enough time to ensure that the external receiver or The error detector can verify the quality of the on-chip Rx with 100% accuracy.

7. DDR5 requires the use of BERT and/or general pattern generators for independent DRAM Rx/Tx testing. This requires a new set of tests, including voltage and frequency sensitivity and stress eye diagram tests, which are not available in DDR3/4. The concept is simple. Anyone should be able to use standardized JEDEC fixtures to perform standard tests to determine the health of DRAM Rx/TX according to the test procedures prescribed by JEDEC.

8. Accurate pressure calibration will become a big problem in DDR5 RX testing, and to obtain an accurate S-parameter model, both must be estimated and measured, including all segments. Another key feature is the ability to accurately or well guess the measurement depth and the oscilloscope record length, so that too much time will not be wasted.

9. DRAM Rx/Tx testing will face huge database management problems. The automation and management of a large number of s-par files, de-embedding models and measurement results will become a nightmare. Imagine that different manufacturers have multiple DIMM configurations and test more than 80 pins at different speed grades. This will be very, very difficult.

Compared with DDR3/4, DDR5 has improved bandwidth, density and channel efficiency. However, the higher the data transfer rate, the faster the signal speed, and the higher the measurement performance that requires conformance testing, debugging, and verification. Tektronix Technology launched the TekExpress DDR5 transmitter solution in July last year, which has improved the degree of automation. Engineers can overcome the analysis challenges brought by various DFEs, using user-defined acquisition and DDR5 de-embedding technology and serial data link analysis SDLA) technology to validate and debug DDR5 designs confidently and efficiently. Understanding the inherent differences of DDR5 helps efficient inspection and debugging.