Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Images are for reference only.

See Product Specifications for product details.

Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Orders over $200 are eligible for a limited edition Chinese-style gift.

Orders over $1000 qualify for a $30 shipping fee waiver.

Orders surpassing $5000 enjoy waived shipping and transaction fees.

These offers are applicable to both new and existing customers and are valid from January 1st, 2024, to December 31st, 2024.

Lattice

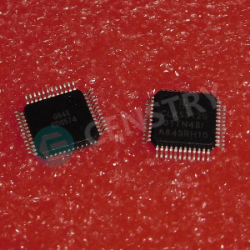

ISPPAC-CLK5312S-01TN48I datasheet

QFP-48

Clock & Timer Ics

Submit your quote request now, and we expect to provide a quote within April 20, 2024. Place your order now, and we expect to complete the transaction within April 24, 2024. Ps:Time is according to GMT+8:00.

ZLG

3374 PCS

ZY2405WRBS-2W .PDF

POWERONE

3947 PCS

ZY1015G-Q1 .PDF

DIODES,ZETEX

3179 PCS

ZXTN5551FTA .PDF

ZETEX

647 PCS

ZXTN3035CLP-7B .PDF

2024-04-19

Great company, nice people, professional ... Thanks to Robin

2024-04-19

Great supplier!

2024-04-19

Great people, great company

2024-04-18

GREAT SUPPLIER ALWAYS DELIVERS ON TIME WITH PRODUCT IN PERFECT CONDITION I WILL ALWAYS BUY FROM THIS COMPANY

2024-04-17

John & Censtry Electronics are A+++

2024-04-14

Highly Recommend Censtry Chips

2024-04-09

I have bought some switches from them. The package was beautiful and the parts were 100% perfect. Thank you.

2024-03-29

Issue resolved

2024-03-08

Jason is the MAN. I had a small crystal order that is crucial to my OEM. Jason went out of his way to get them confirmed & to help me out tremendously. THANK YOU FOR YOUR HARD WORK!!!! We appreciate it & will be giving you as much biz as we can in the future!!!! Thanks Jason!!!!!

2024-01-25

June and Camille are pros, great customer & a joy to work with, we look forward to the next opportunity ;-)

We highly value your feedback. Please share your most genuine review.

*Kindly log in to your account before posting a comment