Published :11/12/2019 8:43:58 PM

Click Count:2103

The LDPC code is well known in the industrial field. It is a packet error correction code with a sparse check matrix proposed by the Massachusetts Institute of Technology Robert Gallager in his doctoral thesis in 1963. It is suitable for almost all channels, and has therefore become a research hotspot in the coding field in recent years. Its performance is close to the Shannon limit, and its description and implementation are simple, easy to carry out theoretical analysis and research, simple decoding and parallel operation, suitable for hardware implementation.

LDPC codes are considered to be the solution to improve error rates in today's 3D TLC and QLC memories. However, they are not suitable for every market.

The Low Density Parity Check (LDPC) code is an error correction code that is used for applications that require efficient information transmission over a channel, with destructive noise such as video broadcasts from satellite or earth transmitters. In the past decade, LDPC codes have received increasing attention in the flash memory field. BCH codes, which are widely used in SLC and MLC flash technologies, do not provide satisfactory performance because today's 3D TLC and 3D QLC flash have limited spare areas and are replaced by other codes that use soft decoding, such as LDPC codes. Although these codes are suitable for some applications, they have two major drawbacks.

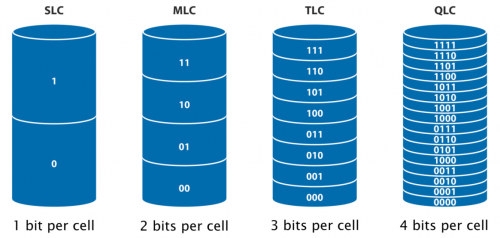

Figure 1: Different types of flash memory currently available

The more bits that are stored in each cell, the lower the data retention and the greater the number of fault bits. Although SLC and MLC are primarily manufactured using planar flash technology, TLC and QLC are manufactured using 3D technology.

LDPC performs well in some areas, but only averages in other areas

LDPC codes show excellent performance for input data with high error rates. Few other codes achieve this level of performance because it is even close to the theoretical maximum Shannon limit. On the other hand, their performance is common for input data with almost no errors. For a few input errors, the failed error correction is very frequent - other code achieves significantly better results in this regard. Therefore, the LDPC code is used for an occasional error in the case of a low input error rate, but requires high performance with a high error rate, for example, the terrestrial digital video broadcasting standard DVB-T. In this case, the failed correction will result in the wrong color of several pixels in the video stream - this is acceptable. For another case - a lot of errors in the input data - the video stream will remain uninterrupted for as long as possible (eg black screen).

This pros and cons explain the emergence of LDPC codes in NAND flash controllers. The latest NAND flash technology shows a very high error rate - especially for the consumer market. LDPC codes are close to the ideal conditions for meeting these requirements. However, there are other market occasional errors that are unacceptable for input data with low error rates. The industrial market is one of them. A common standard for system-level reliability is the JEDEC Enterprise Specification: it requires a rate of less than 10-16 frame errors for the entire working life. Impressively, the performance of the LDPC code is close to the lifetime of the NAND flash, but it does not meet this requirement during the lifetime of the memory, ie the bit error rate of the flash as an error correction input - low at the beginning, at High at the end of life.

LDPC performance can only be estimated

In response to this demanding specification of JEDEC, the University of Applied Sciences and Hyperstone have developed different error correction codes based on Generalized Concatenated Code (GCC). In terms of high input error rate, its performance does not exceed the LDPC code. However, it does show significantly better performance for low and medium error rates. The main advantage is that performance can be calculated so that all input error rates are guaranteed, while LDPC performance can only be estimated for low and medium error rates. For a detailed description of this, please refer to our reliable flash storage basic white paper "Error Correction Code" which we can download for free. This means that in addition to the general performance of low to medium input error rates, it is unclear what exact level performance LDPC will provide. This fact completely prevents it from being used in the industrial and enterprise storage markets.

Figure 2: Hyperstone's latest SSD controllers meet the highest demands for application reliability

The highest required error correction function

GCC-based error correction in Hyperstone's latest flash controllers works closely with a mechanism called calibration. This mechanism ensures that the readout voltage of the flash cell is always in an optimal position, resulting in a low to medium bit error rate over the life of the flash. Therefore, the amount of data error at the input of the error correction unit remains under optimal input conditions - GCC error correction is significantly better than LDPC based error correction conditions. Although calibration combined with GCC improves system-level performance, it does not improve LDPC-based error correction because it shifts the input error rate from a favorable range to a less favorable range for LDPC.

The LDPC code is a common code in the error correction of the flash controller. They are ideal for consumer products that accept sporadic errors. In industrial markets where reliability is critical, they are simply not suitable. Combined with advanced calibration, GCC can easily meet the demanding requirements of the industrial market.